## LAMPIRAN I

## DATA SHEET ATMEGA 8535

#### Features

High-performance, Low-power AVR® 8-bit Microcontroller Advanced RISC Architecture

130 Powerful Instructions – Most Single Clock Cycle Execution

- 32 x 8 General Purpose Working Registers

- Fully Static Operation

- Up to 16 MIPS Throughput at 16 MHz

- On-chip 2-cycle Multiplier

Nonvolatile Program and Data Memories

- 8K Bytes of in-System Self-Programmable Flash Endurance: 10,000 Write/Erase Cycles

- Optional Boot Code Section with Independent Lock Bits In-System Programming by On-chip Boot Program True Read-While-Write Operation

- 512 Bytes EEPROM

Endurance: 100,000 Write/Erase Cycles

- 512 Bytes Internal SRAM

- Programming Lock for Software Security

### **Peripheral Features**

- Two 8-bit Timer/Counters with Separate Prescalers and Compare Modes

- One 16-bit Timer/Counter with Separate Prescaler, Compare Mode, and Capture Mode

- Real Time Counter with Separate Oscillator

- Four PWM Channels

- 8-channel, 10-bit ADC

- 8 Single-ended Channels

- 7 Differential Channels for TQFP Package Only

- 2 Differential Channels with Programmable Gain at 1x, 10x, or 200x for TQFP **Package Only**

- Byte-oriented Two-wire Serial Interface

- Programmable Serial USART

- Master/Slave SPI Serial interface

- Programmable Watchdog Timer with Separate On-chip Oscillator

- On-chip Analog Comparator

### Special Microcontroller Features

- Power-on Reset and Programmable Brown-out Detection

- Internal Calibrated RC Oscillator

- External and internal interrupt Sources

- Six Sleep Modes: Idle, ADC Noise Reduction, Power-save, Power-down, Standby and Extended Standby

### VO and Packages

- 32 Programmable I/O Lines

- 40-pin PDIP, 44-lead TQFP, 44-lead PLCC, and 44-pad QFN/MLF

### **Operating Voltages**

- 2.7 5.5V for ATmega8535L

- 4.5 5.5V for ATmega8535

#### **Speed Grades**

- 0 8 MHz for ATmega8535L

- 0 16 MHz for ATmega8535

8-bit AVR® Microcontroller with 8K Bytes In-System **Programmable** Flash

ATmega8535 ATmega8535L

2502K-AVR-10/06

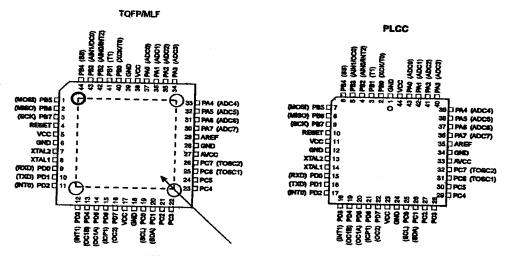

## Pin Configurations

Figure 1. Pinout ATmega8535

NOTE: MLF Bottom pad should be soldered to ground.

)isclaimer

Typical values contained in this data sheet are based on simulations and characterization of other AVR microcontrollers manufactured on the same process technology. Min and Max values will be available after the device is characterized.

ATmega8535(L)

www.DataSheatALisam

### Overview

The ATmega8535 is a low-power CMOS 8-bit microcontroller based on the AVR enhanced RISC architecture. By executing instructions in a single clock cycle, the ATmega8535 achieves throughputs approaching 1 MIPS per MHz allowing the system designer to optimize power consumption versus processing speed.

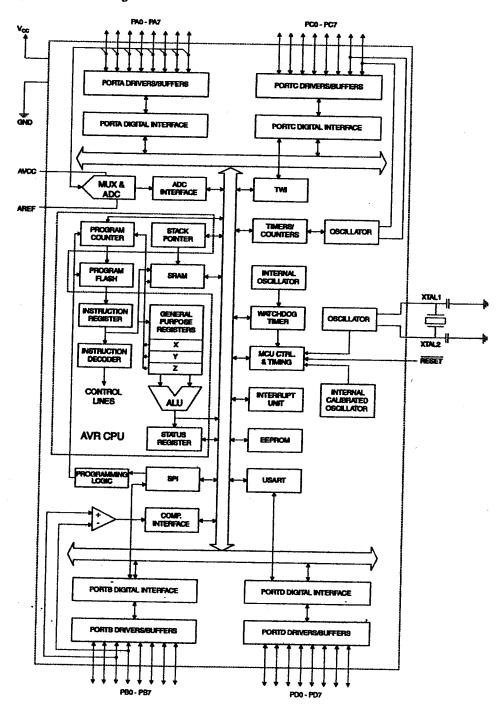

### **Block Diagram**

Figure 2. Block Diagram

The AVR core combines a rich instruction set with 32 general purpose working registers. All 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The ATmega8535 provides the following features: 8K bytes of In-System Programmable Flash with Read-While-Write capabilities, 512 bytes EEPROM, 512 bytes SRAM, 32 general purpose I/O lines, 32 general purpose working registers, three flexible Timer/Counters with compare modes, internal and external interrupts, a serial programmable USART, a byte oriented Two-wire Serial Interface, an 8-channel, 10-bit ADC with optional differential input stage with programmable gain in TQFP package, a programmable Watchdog Timer with Internal Oscillator, an SPI serial port, and six software selectable power saving modes. The Idle mode stops the CPU while allowing the SRAM, Timer/Counters, SPI port, and interrupt system to continue functioning. The Power-down mode saves the register contents but freezes the Oscillator, disabling all other chip functions until the next interrupt or Hardware Reset. In Power-save mode, the asynchronous timer continues to run, allowing the user to maintain a timer base while the rest of the device is sleeping. The ADC Noise Reduction mode stops the CPU and all I/O modules except asynchronous timer and ADC, to minimize switching noise during ADC conversions. In Standby mode, the crystal/resonator Oscillator is running while the rest of the device is sleeping. This allows very fast start-up combined with low-power consumption. In Extended Standby mode, both the main Oscillator and the asynchronous timer continue to run.

The device is manufactured using Atmel's high density nonvolatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System through an SPI serial interface, by a conventional nonvolatile memory programmer, or by an On-chip Boot program running on the AVR core. The boot program can use any interface to download the application program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable Flash on a monolithic chip, the Atmel ATmega8535 is a powerful microcontroller that provides a highly flexible and cost effective solution to many embedded control applications.

The ATmega8535 AVR is supported with a full suite of program and system development tools including: C compilers, macro assemblers, program debugger/simulators, In-Circuit Emulators, and evaluation kits.

## T90S8535 Compatibility

The ATmega8535 provides all the features of the AT90S8535. In addition, several new features are added. The ATmega8535 is backward compatible with AT90S8535 in most cases. However, some incompatibilities between the two microcontrollers exist. To solve this problem, an AT90S8535 compatibility mode can be selected by programming the S8535C fuse. ATmega8535 is pin compatible with AT90S8535, and can replace the AT90S8535 on current Printed Circuit Boards. However, the location of fuse bits and the electrical characteristics differs between the two devices.

# T90S8535 Compatibility lode

Programming the S8535C fuse will change the following functionality:

- The timed sequence for changing the Watchdog Time-out period is disabled. See "Timed Sequences for Changing the Configuration of the Watchdog Timer" on page 45 for details.

- The double buffering of the USART Receive Register is disabled. See "AVR USART vs. AVR UART Compatibility" on page 146 for details.

## ATmega8535(L)

### Pin Descriptions

Vcc

Digital supply voltage.

GND

Ground.

Port A (PA7..PA0)

Port A serves as the analog inputs to the A/D Converter.

Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega8535 as listed on page 60.

Port C (PC7..PC0)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D (PD7..PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega8535 as listed on page 64.

Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 15 on page 37. Shorter pulses are not guaranteed to generate a reset.

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

Output from the inverting Oscillator amplifier.

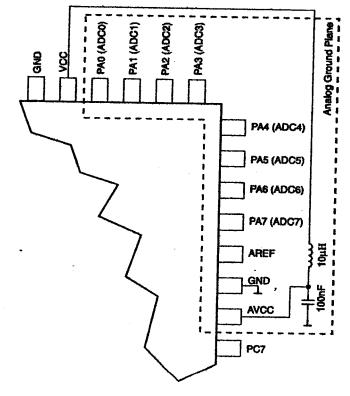

AVCC is the supply voltage pin for Port A and the A/D Converter. It should be externally connected to  $V_{CC}$ , even if the ADC is not used. If the ADC is used, it should be connected to  $V_{CC}$  through a low-pass filter.

AREF is the analog reference pin for the A/D Converter.

REF

RESET

**CTAL1**

TAL2

VCC

02K-AVR-10/06

#### I/O-Ports

#### Introduction

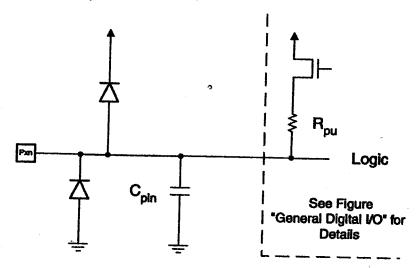

All AVR ports have true Read-Modify-Write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without unintentionally changing the direction of any other pin with the SBI and CBI instructions. The same applies when changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input). Each output buffer has symmetrical drive characteristics with both high sink and source capability. The pin driver is strong enough to drive LED displays directly. All port pins have individually selectable pull-up resistors with a supply-voltage invariant resistance. All I/O pins have protection diodes to both V<sub>CC</sub> and Ground as indicated in Figure 22. Refer to "Electrical Characteristics" on page 255 for a complete list of parameters.

Figure 22. I/O Pin Equivalent Schematic

All registers and bit references in this section are written in general form. A lower case "x" represents the numbering letter for the port, and a lower case "n" represents the bit number. However, when using the register or bit defines in a program, the precise form must be used. For example, PORTB3 for bit no. 3 in Port B, here documented generally as PORTxn. The physical I/O Registers and bit locations are listed in "Register Description for I/O-Ports" on page 66.

Three I/O memory address locations are allocated for each port, one each for the Data Register – PORTx, Data Direction Register – DDRx, and the Port Input Pins – PINx. The Port Input Pins I/O location is read only, while the Data Register and the Data Direction Register are read/write. In addition, the Pull-up Disable – PUD bit in SFIOR disables the pull-up function for all pins in all ports when set.

Using the I/O port as General Digital I/O is described in "Ports as General Digital I/O" on page 52. Most port pins are multiplexed with alternate functions for the peripheral features on the device. How each alternate function interferes with the port pin is described in "Alternate Port Functions" on page 57. Refer to the individual module sections for a full description of the alternate functions.

Note that enabling the alternate function of some of the port pins does not affect the use of the other pins in the port as general digital I/O.

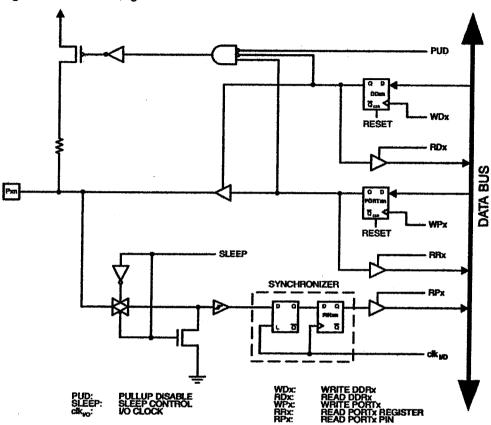

# Ports as General Digital

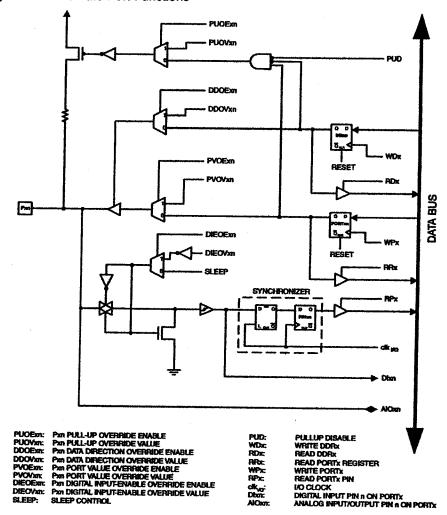

The ports are bi-directional I/O ports with optional internal pull-ups. Figure 23 shows a functional description of one I/O-port pin, here generically called Pxn.

Figure 23. General Digital I/O(1)

Note: 1. WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk<sub>VO</sub>, SLEEP, and PUD are common to all ports.

#### Configuring the Pin

Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in "Register Description for I/O-Ports" on page 66, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output pin. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written a logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic zero or the pin has to be configured as an output pin. The port pins are tri-stated when a reset condition becomes active, even if no clocks are running.

If PORTxn is written a logic one when the pin is configured as an output pin, the port pin is driven high (one). If PORTxn is written a logic zero when the pin is configured as an output pin, the port pin is driven low (zero).

When switching between tri-state ({DDxn, PORTxn} = 0b00) and output high ({DDxn, PORTxn} = 0b11), an intermediate state with either pull-up enabled ({DDxn, PORTxn} =

ATmega8535(L)

www.DataSheatALisan

0b01) or output low ({DDxn, PORTxn} = 0b10) must occur. Normally, the pull-up enabled state is fully acceptable, as a high-impedant environment will not notice the difference between a strong high driver and a pull-up. If this is not the case, the PUD bit in the SFIOR Register can be set to disable all pull-ups in all ports.

Switching between input with pull-up and output low generates the same problem. The user must use either the tri-state ( $\{DDxn, PORTxn\} = 0b00$ ) or the output high state ( $\{DDxn, PORTxn\} = 0b10$ ) as an intermediate step.

Table 21 summarizes the control signals for the pin value.

Table 21. Port Pin Configurations

| DDxn | PORTxn | PUD<br>(in SFIOR) | VO     | Pull-up | Comment                                     |

|------|--------|-------------------|--------|---------|---------------------------------------------|

| 0    | 0      | X                 | Input  | No      | Tri-state (Hi-Z)                            |

| 0    | 1      | 0                 | Input  | Yes     | Pxn will source current if ext. pulled low. |

| 0    | 1      | 1                 | Input  | No      | Tri-state (Hi-Z)                            |

| 1    | 0      | X                 | Output | No      | Output Low (Sink)                           |

| 1    | 1      | х                 | Output | No      | Output High (Source)                        |

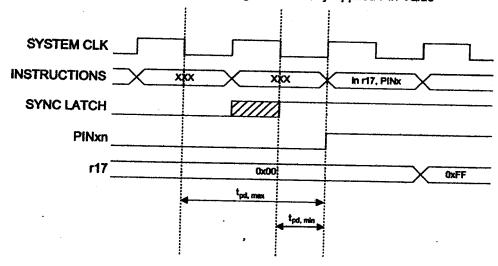

Independent of the setting of Data Direction bit DDxn, the port pin can be read through the PINxn Register bit. As shown in Figure 23, the PINxn Register bit and the preceding latch constitute a synchronizer. This is needed to avoid metastability if the physical pin changes value near the edge of the internal clock, but it also introduces a delay. Figure 24 shows a timing diagram of the synchronization when reading an externally applied pin value. The maximum and minimum propagation delays are denoted  $t_{pd,max}$  and  $t_{pd,min}$  respectively.

Figure 24. Synchronization when Reading an Externally Applied Pin Value

Consider the clock period starting shortly *after* the first falling edge of the system clock. The latch is closed when the clock is low, and goes transparent when the clock is high, as indicated by the shaded region of the "SYNC LATCH" signal. The signal value is latched when the system clock goes low. It is clocked into the PINxn Register at the suc-

53 www.DataSheet4U.com

2K-AVR-10/06

Reading the Pin Value

ceeding positive clock edge. As indicated by the two arrows  $t_{pd,max}$  and  $t_{pd,min}$ , a single signal transition on the pin will be delayed between ½ and 1½ system clock period depending upon the time of assertion.

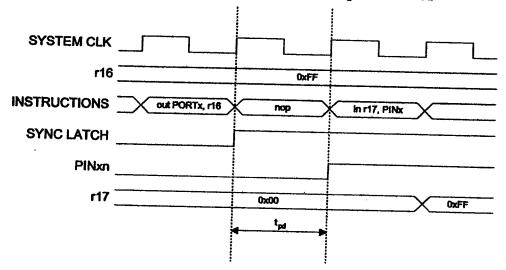

When reading back a software assigned pin value, a *nop* instruction must be inserted as indicated in Figure 25. The *out* instruction sets the "SYNC LATCH" signal at the positive edge of the clock. In this case, the delay  $t_{pd}$  through the synchronizer is one system clock period.

Figure 25. Synchronization when Reading a Software Assigned Pin Value

ATmega8535(L)

www.Data&kent/ALIcam

The following code example shows how to set port B pins 0 and 1 high, 2 and 3 low, and define the port pins from 4 to 7 as input with pull-ups assigned to port pins 6 and 7. The resulting pin values are read back again, but as previously discussed, a *nop* instruction is included to be able to read back the value recently assigned to some of the pins.

```

Assembly Code Example (1)

; Define pull-ups and set outputs high

; Define directions for port pins

r16,(1<<PB7)|(1<<PB6)|(1<<PB1)|(1<<PB0)

ldi

r17,(1<<DDB3)|(1<<DDB2)|(1<<DDB1)|(1<<DDB0)

OUT

PORTB.r16

DDRB.r17

out

; Insert nop for synchronization

; Read port pins

r16.PINB

C Code Example

unsigned char i;

/* Define pull-ups and set outputs high */

/* Define directions for port pins */

PORTB = (1 << PB7) | (1 << PB6) | (1 << PB1) | (1 << PB0);

DDRB = (1 << DDB3) | (1 << DDB2) | (1 << DDB1) | (1 << DDB0);

/* Insert nop for synchronization*/

_NOP();

/* Read port pins */

i = PINB:

```

Note:

For the assembly program, two temporary registers are used to minimize the time from pull-ups are set on pins 0, 1, 6, and 7, until the direction bits are correctly set, defining bits 2 and 3 as low and redefining bits 0 and 1 as strong high drivers.

igital Input Enable and Sleep lodes

As shown in Figure 23, the digital input signal can be clamped to ground at the input of the Schmitt Trigger. The signal denoted SLEEP in the figure, is set by the MCU sleep controller in Power-down mode, Power-save mode, Standby mode, and Extended Standby mode to avoid high power consumption if some input signals are left floating, or have an analog signal level close to  $V_{\rm CC}/2$ .

SLEEP is overridden for port pins enabled as External Interrupt pins. If the External Interrupt Request is not enabled, SLEEP is active also for these pins. SLEEP is also overridden by various other alternate functions as described in "Alternate Port Functions" on page 57.

If a logic high level ("one") is present on an Asynchronous External Interrupt pin configured as "Interrupt on Rising Edge, Falling Edge, or Any Logic Change on Pin" while the external interrupt is *not* enabled, the corresponding External Interrupt Flag will be set

when resuming from the above mentioned sleep modes, as the clamping in these sleep modes produces the requested logic change.

### Unconnected pins

If some pins are unused, it is recommended to ensure that these pins have a defined level. Even though most of the digital inputs are disabled in the deep sleep modes as described above, floating inputs should be avoided to reduce current consumption in all other modes where the digital inputs are enabled (Reset, Active mode and Idle mode).

The simplest method to ensure a defined level of an unused pin, is to enable the internal pull-up. In this case, the pull-up will be disabled during reset. If low power consumption during reset is important, it is recommended to use an external pull-up or pull-down. Connecting unused pins directly to  $V_{CC}$  or GND is not recommended, since this may cause excessive currents if the pin is accidentally configured as an output.

ATmega8535(L)

www.DataSchertAUicom

### **Alternate Port Functions**

Most port pins have alternate functions in addition to being general digital I/Os. Figure 26 shows how the port pin control signals from the simplified Figure 23 can be overridden by alternate functions. The overriding signals may not be present in all port pins, but the figure serves as a generic description applicable to all port pins in the AVR microcontroller family.

Figure 26. Alternate Port Functions<sup>(1)</sup>

Note: 1. WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk<sub>VO</sub>, SLEEP, and PUD are common to all ports. All other signals are unique for each pin.

Table 22 summarizes the function of the overriding signals. The pin and port indexes from Figure 26 are not shown in the succeeding tables. The overriding signals are generated internally in the modules having the alternate function.

Table 22. Generic Description of Overriding Signals for Alternate Functions

| Signal |                                            | The state of the s |

|--------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name   | Full Name                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PUOE   | Pull-up Override<br>Enable                 | If this signal is set, the pull-up enable is controlled by the PUOV signal. If this signal is cleared, the pull-up is enabled when {DDxn, PORTxn, PUD} = 0b010.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PUOV   | Pull-up Override<br>Value                  | If PUOE is set, the pull-up is enabled/disabled when PUOV is set/cleared, regardless of the setting of the DDxn, PORTxn, and PUD Register bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DDOE   | Data Direction<br>Override Enable          | If this signal is set, the Output Driver Enable is controlled by the DDOV signal. If this signal is cleared, the Output driver is enabled by the DDxn Register bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DDOV   | Data Direction<br>Override Value           | If DDOE is set, the Output Driver is enabled/disabled when DDOV is set/cleared, regardless of the setting of the DDxn Register bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PVOE   | Port Value<br>Override Enable              | If this signal is set and the Output Driver is enabled, the port value is controlled by the PVOV signal. If PVOE is cleared, and the Output Driver is enabled, the port Value is controlled by the PORTxn Register bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PVOV   | Port Value<br>Override Value               | If PVOE is set, the port value is set to PVOV, regardless of the setting of the PORTxn Register bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DIEOE  | Digital Input<br>Enable Override<br>Enable | If this bit is set, the Digital Input Enable is controlled by the DIEOV signal. If this signal is cleared, the Digital Input Enable is determined by MCU-state (Normal mode, sleep modes).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DIEOV  | Digital Input<br>Enable Override<br>Value  | If DIEQE is set, the Digital Input is enabled/disabled when DIEOV is set/cleared, regardless of the MCU state (Normal mode, sleep modes).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| DI     | Digital Input                              | This is the Digital Input to alternate functions. In the figure, the signal is connected to the output of the schmitt trigger but before the synchronizer. Unless the Digital Input is used as a clock source, the module with the alternate function will use its own synchronizer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| AIO    | Analog<br>Input/output                     | This is the Analog Input/Output to/from alternate functions. The signal is connected directly to the pad, and can be used bi-directionally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

The following subsections shortly describe the alternate functions for each port, and relate the overriding signals to the alternate function. Refer to the alternate function description for further details.

ATmega8535(L)

www.DatasheatAlicam

## Special Function IO Register –

| Bit           | 7     | 6    | 5     | 4 | 3    | 2   | 1    | 0     |       |

|---------------|-------|------|-------|---|------|-----|------|-------|-------|

|               | AOTS2 | ADTS | ADTSO |   | ACME | PUD | PSR2 | PSRIO | SFIOR |

| Read/Write    | P/W   | P/W  | R/W   | R | R/W  | R/W | R/W  | P/W   |       |

| Initial Value | 0     | ď    | 0     | 0 | 0    | O   | 0    | 0     |       |

#### • Bit 2 -- PUD: Pull-up disable

When this bit is written to one, the pull-ups in the I/O ports are disabled even if the DDxn and PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01). See "Configuring the Pin" on page 52 for more details about this feature.

#### Alternate Functions of Port A

Port A has an alternate function as analog input for the ADC as shown in Table 23. If some Port A pins are configured as outputs, it is essential that these do not switch when a conversion is in progress. This might corrupt the result of the conversion.

Table 23. Port A Pins Alternate Functions

| Port Pin | Alternate Function         |

|----------|----------------------------|

| PA7      | ADC7 (ADC input channel 7) |

| PA6      | ADC6 (ADC input channel 6) |

| PA5      | ADC5 (ADC input channel 5) |

| PA4      | ADC4 (ADC input channel 4) |

| PA3      | ADC3 (ADC input channel 3) |

| PA2      | ADC2 (ADC input channel 2) |

| PA1      | ADC1 (ADC input channel 1) |

| PAO      | ADC0 (ADC input channel 0) |

Table 24 and Table 25 relate the alternate functions of Port A to the overriding signals shown in Figure 26 on page 57.

Table 24. Overriding Signals for Alternate Functions in PA7..PA4

| Signal Name | PA7/ADC7   | PA6/ADC6   | PA5/ADC5   | PA4/ADC4   |

|-------------|------------|------------|------------|------------|

| PUOE        | Ø          | 0          | Ó          | 0          |

| PUOV        | 0          | 0          | 0          | 0          |

| DDOE        | 0          | 0          | 0          | 0          |

| DDOV        | Q          | 0          | 0          | 0          |

| PVOE        | 0          | 0          | 0          | 0          |

| PVOV        | 0          | 0          | 0          | 0          |

| DIEOE       | 0          | 0          | 0          | 0          |

| DIEOV       | 0          | 0 -        | 0          | 0          |

| DI          | _          | -          | _          | -          |

| AIO         | ADC7 INPUT | ADC6 INPUT | ADC5 INPUT | ADC4 INPUT |

Table 25. Overriding Signals for Alternate Functions in PA3..PA0

| Signal Name | PA3/ADC3   | PA2/ADC2   | PA1/ADC1   | PA0/ADC0   |

|-------------|------------|------------|------------|------------|

| PUOE        | 0          | Ö          | 0          | 0          |

| PUOV        | 0          | 0          | 0          | 0          |

| DDOE        | 0          | 0          | 0          | 0          |

| DDOV        | Ó          | 0          | 0          | 0          |

| PVOE        | 0          | 0          | 0          | 0          |

| PVOV        | 0          | 0          | 0          | 0          |

| DIEOE.      | 0          | 0          | 0          | 0          |

| DIEOV       | 0          | 0          | 0          | 0          |

| Di          | -          | -          |            | _          |

| AIO         | ADC3 INPUT | ADC2 INPUT | ADC1 INPUT | ADC0 INPUT |

#### Alternate Functions Of Port B

The Port B pins with alternate functions are shown in Table 26.

Table 26. Port B Pins Alternate Functions

| Port Pin | Alternate Functions                                                                      |

|----------|------------------------------------------------------------------------------------------|

| PB7      | SCK (SPI Bus Serial Clock)                                                               |

| PB6      | MISO (SPI Bus Master Input/Slave Output)                                                 |

| PB5      | MOSI (SPI Bus Master Output/Slave Input)                                                 |

| PB4      | SS (SPI Slave Select Input)                                                              |

| PB3      | AIN1 (Analog Comparator Negative Input) OC0 (Timer/Counter0 Output Compare Match Output) |

| PB2      | AIN0 (Analog Comparator Positive Input) INT2 (External Interrupt 2 Input)                |

| PB1      | T1 (Timer/Counter1 External Counter Input)                                               |

| PB0      | T0 (Timer/Counter0 External Counter Input) XCK (USART External Clock Input/Output)       |

The alternate pin configuration is as follows:

#### · SCK - Port B, Bit 7

SCK: Master Clock output, Slave Clock input pin for SPI channel. When the SPI is énabled as a Slave, this pin is configured as an input regardless of the setting of DDB7. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB7. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB7 bit.

#### . MISO - Port B, Bit 6

MISO: Master Data input, Slave Data output pin for SPI channel. When the SPI is enabled as a Master, this pin is configured as an input regardless of the setting of DDB6. When the SPI is enabled as a Slave, the data direction of this pin is controlled by DDB6. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB6 bit.

ATmega8535(L)

www.DataSheetALigam

### . MOSI - Port B, Bit 5

MOSI: SPI Master Data output, Slave Data input for SPI channel. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB5. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB5. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB5 bit.

## • SS - Port B, Bit 4

SS: Slave Select input. When the SPI is enabled as a Slave, this pin is configured as an input regardless of the setting of DDB4. As a Slave, the SPI is activated when this pin is driven low. When the SPI is enabled as a Master, the data direction of this pin is controlled by DDB4. When the pin is forced by the SPI to be an input, the pull-up can still be controlled by the PORTB4 bit.

#### • AIN1/OC0 - Port B, B計 3

AIN1, Analog Comparator Negative input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the Analog Comparator.

OC0, Output Compare Match output: The PB3 pin can serve as an external output for the Timer/Counter0 Compare Match. The PB3 pin has to be configured as an output (DDB3 set (one)) to serve this function. The OC0 pin is also the output pin for the PWM mode timer function.

### AIN0/INT2 - Port B, Bit 2

AINO, Analog Comparator Positive input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the Analog Comparator.

INT2, External Interrupt Source 2: The PB2 pin can serve as an external interrupt source to the MCU.

## • T1 - Port B, Bit 1

T1, Timer/Counter1 Counter Source.

### T0/XCK - Port B, Bit 0

T0, Timer/Counter0 Counter Source.

XCK, USART External Clock. The Data Direction Register (DDB0) controls whether the clock is output (DDB0 set) or input (DDB0 cleared). The XCK pin is active only when the USART operates in synchronous mode.

Table 27 and Table 28 relate the alternate functions of Port B to the overriding signals shown in Figure 26 on page 57. SPI MSTR INPUT and SPI SLAVE OUTPUT constitute the MISO signal, while MOSI is divided into SPI MSTR OUTPUT and SPI SLAVE INPUT.

Table 27. Overriding Signals for Alternate Functions in PB7..PB4

| Signal<br>Name | PB7/SCK      | PB6/MISO         | PB5/MOSI        | PB4/\$\$     |

|----------------|--------------|------------------|-----------------|--------------|

| PUOE           | SPE • MSTR   | SPE • MSTR       | SPE • MSTR      | SPE • MSTR   |

| PUOV           | PORTB7 • PUD | PORTB6 • PUD     | PORTB5 • PUD    | PORTB4 • PUD |

| DDOE           | SPE • MSTR   | SPE • MSTR       | SPE • MSTR      | SPE • MSTR   |

| DDOV           | 0            | 0                | 0               | 0            |

| PVOE           | SPE • MSTR   | SPE • MSTR       | SPE • MSTR      | 0            |

| PVOV           | SCK OUTPUT   | SPI SLAVE OUTPUT | SPI MSTR OUTPUT | 0            |

| DIEOE          | 0            | ٥                | 0               | 0            |

| DIEOV          | 0            | 0                | 0               | 0            |

| DI             | SCK INPUT    | SPI MSTR INPUT   | SPI SLAVE INPUT | SPI SS       |

| AIO            | -            | _                |                 | _            |

Table 28. Overriding Signals for Alternate Functions in PB3..PB0

| Signal<br>Name | PB3/OC0/AIN1 | PB2/INT2/AIN0 | PB1/T1   | PB0/T0/XCK   |

|----------------|--------------|---------------|----------|--------------|

| PUOE           | 0            | 0             | 0        | 0            |

| PUOV           | 0            | 0             | 0        | 0            |

| DDOE           | 0            | 0             | 0        | 0            |

| DÒOV           | 0            | 0             | 0        | 0            |

| PVOE           | OC0 ENABLE   | 0             | Ó        | UMSEL        |

| PVOV           | OC0          | 0             | 0        | XCK OUTPUT   |

| DIEOE          | Ò            | INT2 ENABLE   | 0        | 0            |

| DIEOV          | 0            | 1             | 0        | 0            |

| ÐI             | _            | INT2 INPUT    | T1 INPUT | XCK INPUT/TO |

| AIO            | AIN1 INPUT   | AINO INPUT    | _        | _            |

### Iternate Functions of Port C

The Port C pins with alternate functions are shown in Table 29.

Table 29. Port C Pins Alternate Functions

| Port Pin | Alternate Function                               |

|----------|--------------------------------------------------|

| PC7      | TOSC2 (Timer Oscillator Pin 2)                   |

| PC6      | TOSC1 (Timer Oscillator Pin 1)                   |

| PC1      | SDA (Two-wire Serial Bus Data Input/Output Line) |

| PC0      | SCL (Two-wire Serial Bus Clock Line)             |

The alternate pin configuration is as follows:

• TOSC2 - Port C, Bit 7

ATmega8535(L)

www.DataShertALican

TOSC2, Timer Oscillator pin 2: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC7 is disconnected from the port, and becomes the inverting output of the Oscillator amplifier. In this mode, a crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

### • TOSC1 - Port C, Bit 6

TOSC1, Timer Oscillator pin 1: When the AS2 bit in ASSR is set (one) to enable asynchronous clocking of Timer/Counter2, pin PC6 is disconnected from the port, and becomes the input of the inverting Oscillator amplifier. In this mode, a crystal Oscillator is connected to this pin, and the pin can not be used as an I/O pin.

### • SDA - Port C, Bit 1

SDA, Two-wire Serial Interface Data: When the TWEN bit in TWCR is set (one) to enable the Two-wire Serial Interface, pin PC1 is disconnected from the port and becomes the Serial Data I/O pin for the Two-wire Serial Interface. In this mode, there is a spike filter on the pin to suppress spikes shorter than 50 ns on the input signal, and the pin is driven by an open drain driver with slew-rate limitation. When this pin is used by the Two-wire Serial Interface, the pull-up can still be controlled by the PORTC1 bit.

#### • SCL - Port C, Bit 0

SCL, Two-wire Serial Interface Clock: When the TWEN bit in TWCR is set (one) to enable the Two-wire Serial Interface, pin PC0 is disconnected from the port and becomes the Serial Clock I/O pin for the Two-wire Serial Interface. In this mode, there is a spike filter on the pin to suppress spikes shorter than 50 ns on the input signal, and the pin is driven by an open drain driver with slew-rate limitation. When this pin is used by the Two-wire Serial Interface, the pull-up can still be controlled by the PORTC0 bit.

Table 30 and Table 31 relaté the alternate functions of Port C to the overriding signals shown in Figure 26 on page 57.

Table 30. Overriding Signals for Alternate Functions in PC7..PC6

| Signal Name | PC7/TOSC2       | PC6/TOSC1      |

|-------------|-----------------|----------------|

| PUOE        | AS2             | AS2            |

| PUOV        | Ó               | 0              |

| DDOE        | AS2             | AS2            |

| DDOV        | 0               | 0              |

| PVOE        | 0               | 0              |

| PVOV        | 0               | 0              |

| DIEOE       | AS2             | AS2            |

| DIEOV       | 0               | 0              |

| DI          | →               |                |

| AIO         | T/C2 OSC OUTPUT | T/C2 OSC INPUT |

TUGAS AKHIR

Table 31. Overriding Signals for Alternate Functions in PC1..PC0(1)

| Signal Name | PC1/SDA      | PC0/SCL      |

|-------------|--------------|--------------|

| PUÒE        | TWEN         | TWEN         |

| PUOV        | PORTC1 • PUD | PORTC0 • PUD |

| DDOE        | TWEN         | TWEN         |

| DDOV        | SDA_OUT      | SCL_OUT      |

| PVOE        | TWEN         | TWEN         |

| PVOV        | 0            | 0            |

| DIÉOE       | 0            | 0            |

| DIEOV       | 0            | 0            |

| DI          | -            | _            |

| AlO         | SDA INPUT    | SCL INPUT    |

Note:

When enabled, the Two-wire Serial Interface enables slew-rate-controls on the output pins PC0 and PC1. This is not shown in the figure. In addition, spike filters are connected between the AlO outputs shown in the port figure and the digital logic of the TWI module.

#### Alternate Functions of Port D

The Port D pins with alternate functions are shown in Table 32.

Table 32. Port D Pins Alternate Functions

| Port Pin | Alternate Function                                  |

|----------|-----------------------------------------------------|

| PD7      | OC2 (Timer/Counter2 Output Compare Match Output)    |

| PD6      | ICP1 (Timer/Counter1 Input Capture Pin)             |

| PD5      | OC1A (Timer/Counter1 Output Compare A Match Output) |

| PD4      | OC1B (Timer/Counter1 Output Compare B Match Output) |

| PD3      | INT1 (External Interrupt 1 Input)                   |

| PD2      | INTO (External Interrupt 0 Input)                   |

| PD1      | TXD (USART Output Pin)                              |

| PD0      | RXD (USART Input Pin)                               |

The alternate pin configuration is as follows:

#### OC2 — Port D. Bit 7

OC2, Timer/Counter2 Output Compare Match output: The PD7 pin can serve as an external output for the Timer/Counter2 Output Compare. The pin has to be configured as an output (DDD7 set (one)) to serve this function. The OC2 pin is also the output pin for the PWM mode timer function.

#### • ICP1 - Port D, Bit 6

ICP1 - Input Capture Pin: The PD6 pin can act as an Input Capture pin for Timer/Counter1.

#### OC1A – Port D, Bit 5

OC1A, Output Compare Match A output: The PD5 pin can serve as an external output for the Timer/Counter1 Output Compare A. The pin has to be configured as an output

ATmega8535(L)

www.DataSheetALisan

(DDD5 set (one)) to serve this function. The OC1A pin is also the output pin for the PWM mode timer function.

#### OC1B – Port D, Bit 4

OC1B, Output Compare Match B output: The PD4 pin can serve as an external output for the Timer/Counter1 Output Compare B. The pin has to be configured as an output (DDD4 set (one)) to serve this function. The OC1B pin is also the output pin for the PWM mode timer function.

#### INT1 – Port D, Bit 3

INT1, External Interrupt Source 1: The PD3 pin can serve as an external interrupt source.

#### INT0 - Port D, Bit 2

INTO, External Interrupt Source 0: The PD2 pin can serve as an external interrupt source.

#### • TXD - Port D, Bit 1

TXD, Transmit Data (Data output pin for the USART). When the USART Transmitter is enabled, this pin is configured as an output regardless of the value of DDD1.

#### RXD - Port D, Bit 0

RXD, Receive Data (Data input pin for the USART). When the USART Receiver is enabled this pin is configured as an input regardless of the value of DDD0. When the USART forces this pin to be an input, the pull-up can still be controlled by the PORTD0 bit.

Table 33 and Table 34 relate the alternate functions of Port D to the overriding signals shown in Figure 26 on page 57.

Table 33. Overriding Signals for Alternate Functions PD7..PD4

| Signal Name | PD7/OC2    | PD6/ICP1   | PD5/OC1A    | PD4/OC1B    |

|-------------|------------|------------|-------------|-------------|

| PUOE        | 0          | 0          | 0           | 0           |

| PUOV        | 0          | 0          | 0           | 0           |

| DDOE        | 0          | 0          | 0           | 0           |

| DDOV        | 0          | 0          | 0           | 0           |

| PVOE        | OC2 ENABLE | ,          | OC1A ENABLE | OC1B ENABLE |

| PVOV        | OC2        | 0          | OC1A        | OC1B        |

| DIEOE       | 0          | 0          | 0           | 0           |

| DIEOV       | 0          | 0          | 0           | 0           |

| DI          | _          | ICP1 INPUT |             |             |

| AIO         | _          | 1_         | _           | 1           |

Table 34. Overriding Signals for Alternate Functions in PD3..PD0

| Signal Name | PD3/INT1    | PD2/INTO    | PD1/TXD | PD0/RXD      |

|-------------|-------------|-------------|---------|--------------|

| PUOE        | 0           | 0           | TXEN    | RXEN         |

| PUOV        | 0           | 0           | 0       | PORTDO • PUD |

| DDOE        | 0           | 0           | TXEN    | RXEN         |

| DDOV        | 0           | 0           | 1       | 0            |

| PVOE        | 0           | 0           | TXEN    | 0            |

| PVOV        | 0           | 0           | TXD     | 0            |

| DIEOE       | INT1 ENABLE | INTO ENABLE | 0       | 0            |

| DIEOV       | 1           | 1           | 0       | 0            |

| DI          | INT1 INPUT  | INTQ INPUT  | _       | RXD          |

| AIO         | _           | _           | _       | -            |

### Register Description for /O-Ports

Port A Data Register – PORTA

| Bit           | 7      | . 6    | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|               | PORTA7 | PORTA6 | PORTA5 | PORTA4 | PORTA3 | PORTA2 | PORTA1 | PORTAD | PORTA |

| Read/Write    | R/W    | P/W    | R/W    | R/W    | P/W    | F/W    | RW     | fw     |       |

| initial Value | 0      | 0      | 0      | 0      | O      | 0      | O      | n      |       |

Port A Data Direction Register DDRA

| Bit           | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|------|------|------|------|------|------|------|------|

|               | DDA7 | DDA6 | DDA5 | DDA4 | DDAS | DDA2 | DDA1 | DDA0 | DDRA |

| Read/Write    | R/W  | R/W  | P/W  | R/W  | R/W  | R/W  | RW   | R/W  | i    |

| Initial Value | .0   | 0    | 0    | 0    | 0    | 0    | ٥    | 0    |      |

ort A Input Pins Address –

| Bit           | . 7   | 6     | 5     | 4     | 3     | 2     | 1     | 0     |      |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

|               | PINA7 | PINA6 | PINA5 | PINA4 | PINA3 | PINA2 | PINA1 | PINAO | PINA |

| Read/Write    | R     | R     | R     | R     | R     | R     | Ŕ     | R     |      |

| Initial Value | NA    | N/A   |      |

ort B Data Register - PORTB

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|-------|

|               | PORTB7 | PORTB6 | PORTB5 | PORTB4 | PORTB3 | PORTB2 | PORTB1 | PORTBO | PORTB |

| ReadWrite     | R/W    | FVW    | R/W    | ŔW     | F/W    | R/W    | R/W    | RW     |       |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | ò      |       |

ort B Data Direction Register

DDRB

| Bit           | 7 -  | 6    | 5    | 4    | 3    | 2    | 1    | 0    |      |

|---------------|------|------|------|------|------|------|------|------|------|

|               | DDB7 | DOB6 | DDB5 | DDB4 | DDB3 | DDB2 | DDB1 | DDB0 | DDRB |

| Read/Write    | F/W  | R/W  | R/W  | R/W  | P/W  | P/W  | F/W  | R/W  | •    |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

ATmega8535(L)

www.DataSheetALlgan

| Port B Input Pins Address –    |               |        |        |          |        |        |        |        |              |       |

|--------------------------------|---------------|--------|--------|----------|--------|--------|--------|--------|--------------|-------|

| PINB                           | Bit           | 7      | 6      | <b>5</b> | 4      | 3      | 2      | , 1    | 0            |       |

|                                |               | PINB7  | PINB6  | PINB5    | PINB4  | PINB3  | PINB2  | PINB1  | PINBO        | PINB  |

|                                | Read/Write    | R      | R      | R        | Ŕ      | R      | Ŕ      | R      | ₽            | ŀ     |

|                                | Initial Value | N/A    | N/A    | N/A      | N/A    | N/A    | N/A    | N/A    | N/A          |       |

| Port C Data Register - PORTC   |               |        |        |          |        |        |        |        |              | •     |

|                                | Bit           | 7      | 6      | 5        | 4      | 3      | 2      | 1      | 0            |       |

| •                              |               | PORTC7 | PORTC6 | PORTC5   | PORTC4 | PORTC3 | PORTC2 | PORTC1 | PORTCO       | PORTC |

|                                | Read/Write    | P/W    | ' R/W  | R/W      | R/W    | R/W    | RW     | 'RW'   | R/W          | ,     |

|                                | Initial Value | 0      | 0      | 0        | 0      | 0      | 0      | 0      | 0            |       |

| Port C Data Direction Register |               |        |        |          |        |        |        |        |              |       |

| - DDRC                         | Bit           | 7      | 6      | 5        | 4      | 3      | 2      |        | 0            |       |

|                                |               | DDC7   | DDC6   | DDC5     | DDC4   | DDC3   | DDC2   | DDC1   | DDC0         | DDRC  |

|                                | Read/Write    | R/W    | R/W    | R/W      | R/W    | R/W    | F/W    | Fl/W   | R/W          |       |

|                                | Initial Value | 0      | 0      | 0        | 0      | 0      | 0      | 0      | 0            |       |

| Port C Input Pins Address -    |               |        |        |          |        |        |        |        |              |       |

| INC                            | Bit           | 7      | 6      | 5        | 4      | 3 (    | 2      | . 1    | 0            |       |

|                                |               | PINC7  | PINC6  | PINC5    | PINC4  | PINC3  | PINC2  | PINC1  | PINCO        | PINC  |

|                                | Read/Write    | R      | R      | Ŕ        | R      | R      | R      | R      | R            |       |

|                                | Initial Value | N/A    | N/A    | N/A      | N/A    | N/A    | N/A    | N/A    | N/A          |       |

| Port D Data Register - PORTD   |               |        |        |          |        |        |        |        |              |       |

| -                              | Bit .         | 7      | 6,     | 5        | 4      | 3 ,    | 2      | 1      | 0            |       |

|                                |               | PORTO7 | PORTD6 | PORTD5   | PORTD4 | PORTD3 | PORTD2 | PORTD1 | PORTDO       | PORTD |

|                                | Read/Write    | R/W    | P/W    | R/W      | R/W    | R/W    | R/W    | R/W    | P/W          |       |

|                                | Initial Value | 0      | 0      | Q        | 0      | 0      | 0      | 0      | 0            |       |

| ort D Data Direction Register  |               |        |        |          |        |        |        |        |              |       |

| DDRD                           | Bit           | 7      | . 6    | 5        | 4      | 3      | 2      | 1      | 0            |       |

|                                |               | DDD7   | DDD6   | DDD5     | DDD4   | DDD3   | DDD2   | DDD1   | DDD0         | DDRD  |

|                                | Read/Write    | P/W    | P/W    | R/W      | R/W    | ' R/W  | R/W    | R/W    | R/W          |       |

|                                | Initial Value | 0      | 0      | 0        | 0      | O      | Ó      | O      | 0            |       |

| ort D Input Pins Address –     |               |        |        |          |        |        |        |        | ' <u>-</u> - |       |

| IND                            | Bit _         | 7      | 6      | 5        | 4 .    | 3      | 2      | 1      | 0            |       |

|                                | I             | PIND7  | PIND6  | PIND5    | PIND4  | PIND3  | PIND2  | PIND1  | PINDO        | PIND  |

|                                | Read/Write    | R      | ř.     | R        | R      | R      | R      | B      | <u> </u>     | ,     |

Initial Value

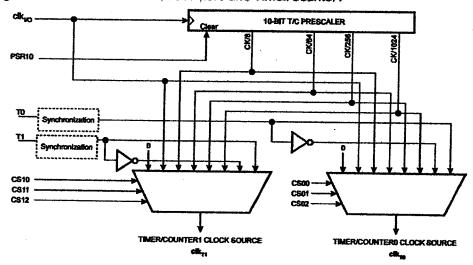

## Timer/Counter0 and Timer/Counter1 Prescalers

Timer/Counter1 and Timer/Counter0 share the same prescaler module, but the Timer/Counters can have different prescaler settings. The description below applies to both Timer/Counter1 and Timer/Counter0.

Internal Clock Source

The Timer/Counter can be clocked directly by the system clock (by setting the CSn2:0 = 1). This provides the fastest operation, with a maximum Timer/Counter clock frequency equal to system clock frequency ( $f_{\text{CLK\_I/O}}$ ). Alternatively, one of four taps from the prescaler can be used as a clock source. The prescaled clock has a frequency of either  $f_{\text{CLK\_I/O}}/8$ ,  $f_{\text{CLK\_I/O}}/64$ ,  $f_{\text{CLK\_I/O}}/256$ , or  $f_{\text{CLK\_I/O}}/1024$ .

Prescaler Reset

The prescaler is free running (i.e., operates independently of the clock select logic of the Timer/Counter) and it is shared by Timer/Counter1 and Timer/Counter0. Since the prescaler is not affected by the Timer/Counter's clock select, the state of the prescaler will have implications for situations where a prescaled clock is used. One example of prescaling artifacts occurs when the timer is enabled and clocked by the prescaler (6 > CSn2:0 > 1). The number of system clock cycles from when the timer is enabled to the first count-occurs can be from 1 to N+1 system clock cycles, where N equals the prescaler divisor (8, 64, 256, or 1024).

It is possible to use the Prescaler Reset for synchronizing the Timer/Counter to program execution. However, care must be taken if the other Timer/Counter that shares the same prescaler also uses prescaling. A prescaler reset will affect the prescaler period for all Timer/Counters it is connected to.

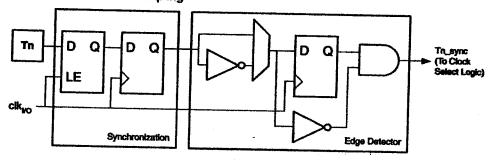

external Clock Source

An external clock source applied to the T1/T0 pin can be used as Timer/Counter clock ( $clk_{T1}/clk_{T0}$ ). The T1/T0 pin is sampled once every system clock cycle by the pin synchronization logic. The synchronized (sampled) signal is then passed through the edge detector. Figure 38 shows a functional equivalent block diagram of the T1/T0 synchronization and edge detector logic. The registers are clocked at the positive edge of the internal system clock ( $clk_{VO}$ ). The latch is transparent in the high period of the internal system clock.

The edge detector generates one  $clk_{T1}/clk_{T0}$  pulse for each positive (CSn2:0 = 7) or negative (CSn2:0 = 6) edge it detects.

Figure 38. T1/T0 Pin Sampling

The synchronization and edge detector logic introduces a delay of 2.5 to 3.5 system clock cycles from an edge has been applied to the T1/T0 pin to the counter is updated.

Enabling and disabling of the clock input must be done when T1/T0 has been stable for at least one system clock cycle, otherwise it is a risk that a false Timer/Counter clock pulse is generated.

Each half period of the external clock applied must be longer than one system clock cycle to ensure correct sampling. The external clock must be guaranteed to have less than half the system clock frequency ( $f_{\rm ExtClk} < f_{\rm clk\_IVO}/2$ ) given a 50/50% duty cycle. Since the edge detector uses sampling, the maximum frequency of an external clock it can detect is half the sampling frequency (Nyquist sampling theorem). However, due to variation of the system clock frequency and duty cycle caused by Oscillator source (crystal, resonator, and capacitors) tolerances, it is recommended that maximum frequency of an external clock source is less than  $f_{\rm clk\_IVO}/2.5$ .

An external clock source can not be prescaled.

Figure 39. Prescaler for Timer/Counter0 and Timer/Counter1(1)

Note: 1. The synchronization logic on the input pins (T1/T0) is shown in Figure 38.

Special Function IO Register— SFIOR

| Bit           | 7     | 6     | 5     | 4 | 3    | 2   | 1    | 0     |       |

|---------------|-------|-------|-------|---|------|-----|------|-------|-------|

|               | ADTS2 | ADTS1 | ADTS0 |   | ACME | PUD | PSR2 | PSR10 | SFIOR |

| Read/Write    | RW    | P/W   | RW    | R | P/W  | R/W | RW   | RW    | •     |

| Initial Value | 0     | 0     | 0     | 0 | 0    | 0   | 0    | 0     |       |

## Bit 0 – PSR10: Prescaler Reset Timer/Counter1 and Timer/Counter0

When this bit is written to one, the Timer/Counter1 and Timer/Counter0 prescaler will be reset. The bit will be cleared by hardware after the operation is performed. Writing a zero to this bit will have no effect. Note that Timer/Counter1 and Timer/Counter0 share the same prescaler and a reset of this prescaler will affect both timers. This bit will always be read as zero.

ATmega8535(L)

www.DateShertAUisem

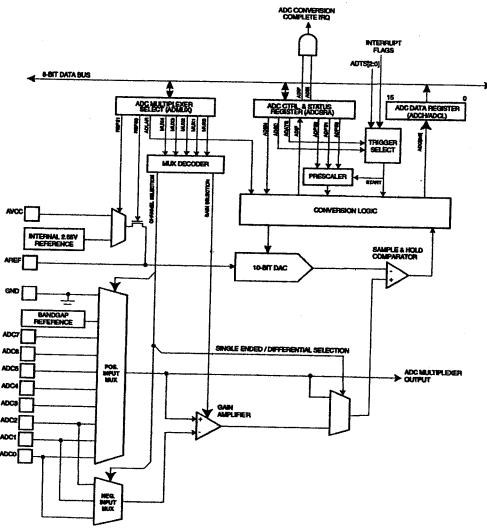

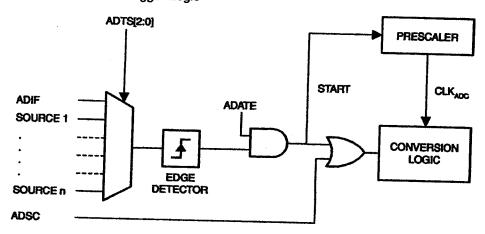

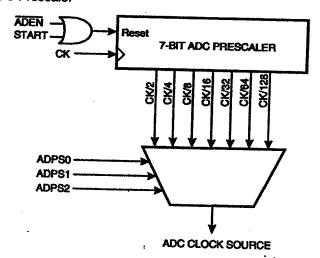

## Analog-to-Digital Converter

Features

- 10-bit Resolution

- 0.5 LSB Integral Non-linearity

- ±2 LSB Absolute Accuracy

- 65 260 µs Conversion Time

- Up to 15 kSPS at Maximum Resolution

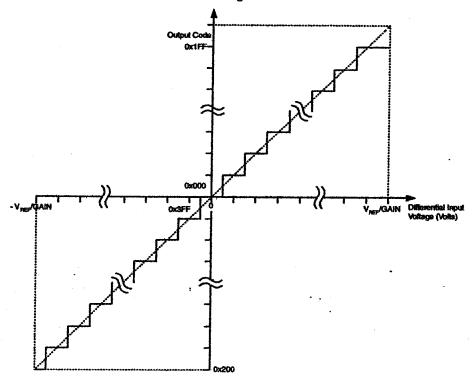

- 8 Multiplexed Single Ended Input Channels

- 7 Differential Input Channels

- 2 Differential Input Channels with Optional Gain of 10x and 200x<sup>(1)</sup>

- Optional Left Adjustment for ADC Result Readout

- 0 V<sub>CC</sub> ADC Input Voltage Range

- Selectable 2.56V ADC Reference Voltage

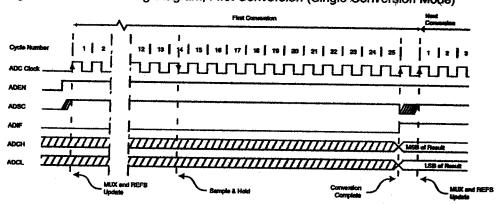

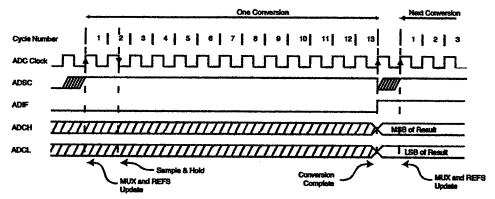

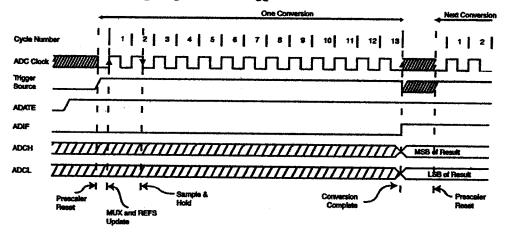

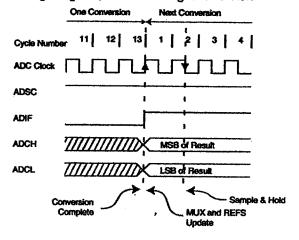

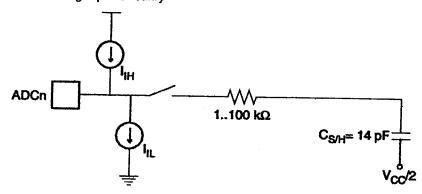

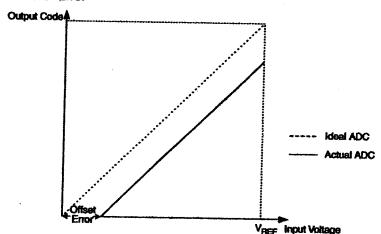

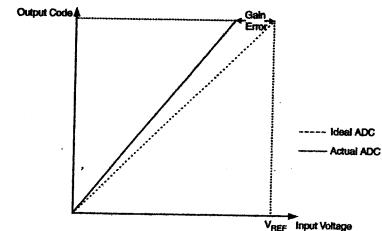

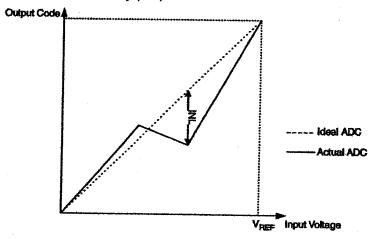

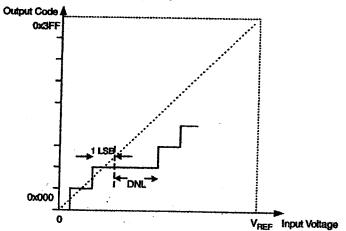

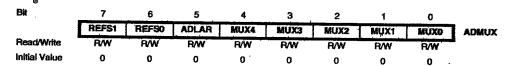

- Free Running or Single Conversion Mode